#### EE 330 Lecture 9

#### **IC** Fabrication Technology

- Crystal Preparation

- Masking

- Photolithographic Process

- Deposition

- Ion Implantation

- Etching

- Diffusion

- Oxidation

- Epitaxy

- Polysilicon

- Planarization

- Contacts, Interconnect and Metalization

#### Fall 2024 Exam Schedule

Exam 1 Friday Sept 27

#### Review from Last Time Design Rules

• Give minimum feature sizes, spacing, and other constraints that are acceptable in a process

• Very large number of devices can be reliably made with the design rules of a process

• Yield and performance unpredictable and often low if rules are violated

Compatible with design rule checker in integrated toolsets

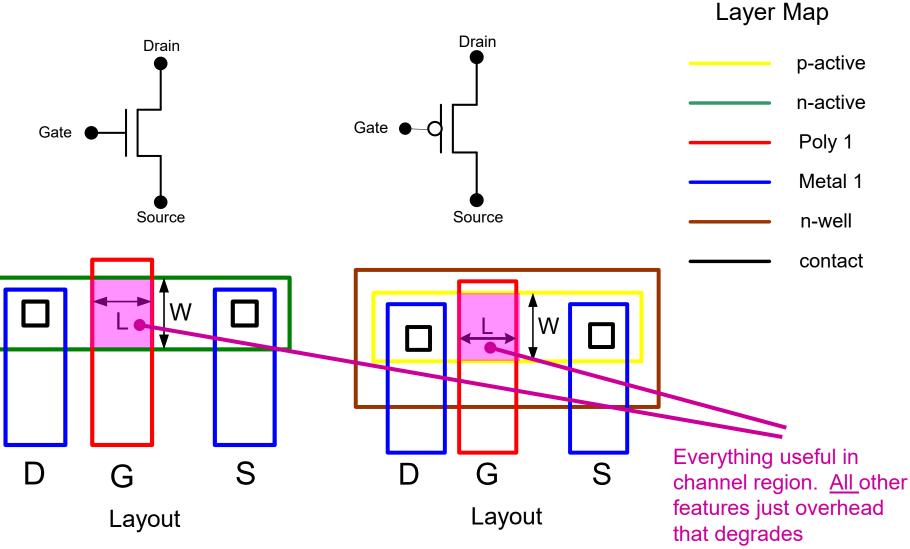

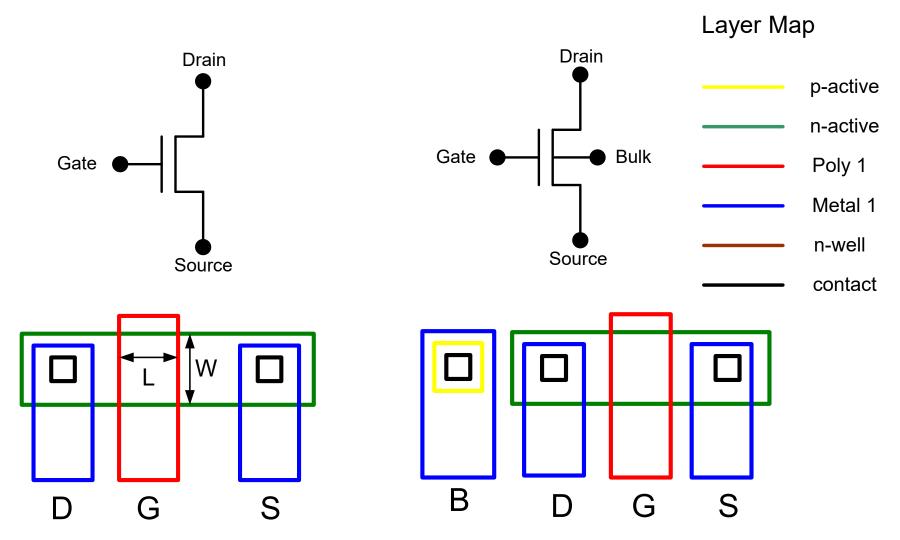

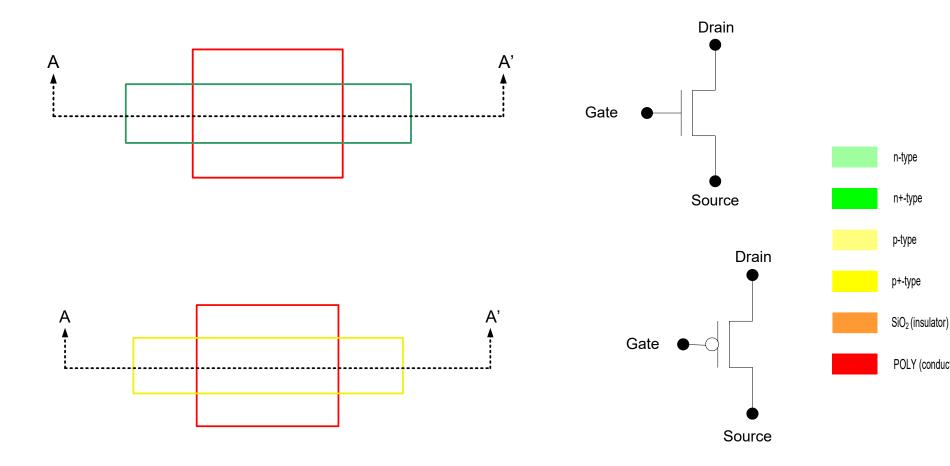

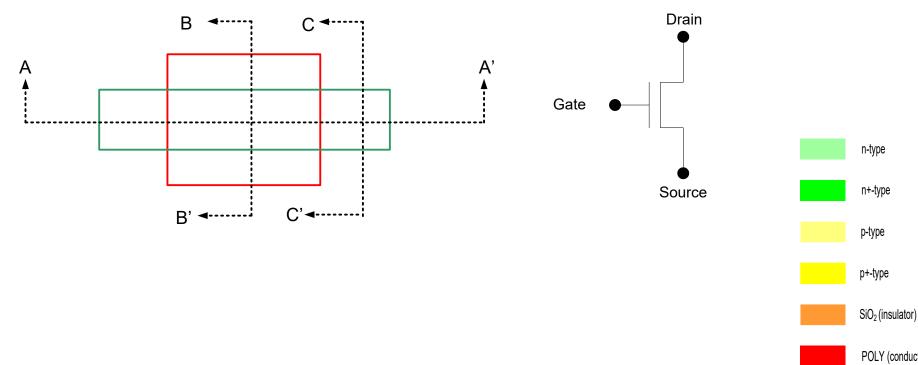

### Design Rules and Layout – consider transistors

performance

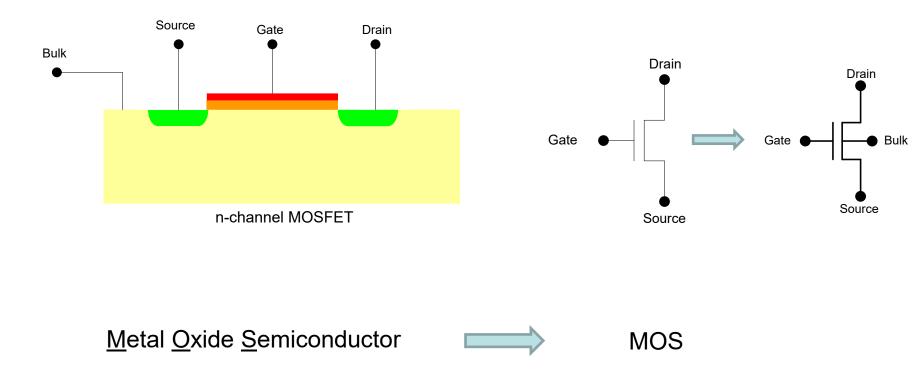

#### **Review from Last Time** MOS Transistor Nomenclature

Early processes used metal for the gate, today metal is seldom used but the term MOS transistor is standard even though the gate is no longer metal

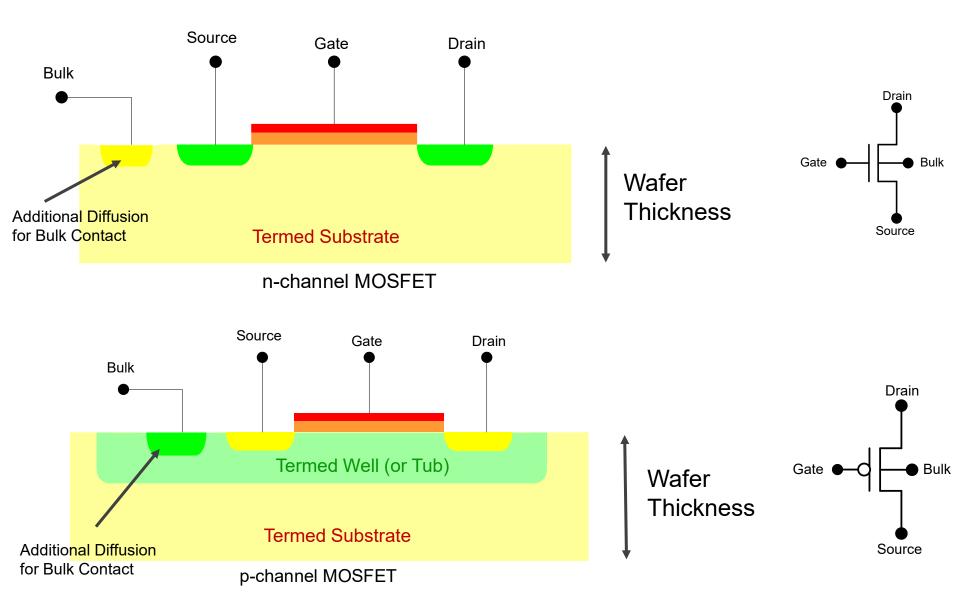

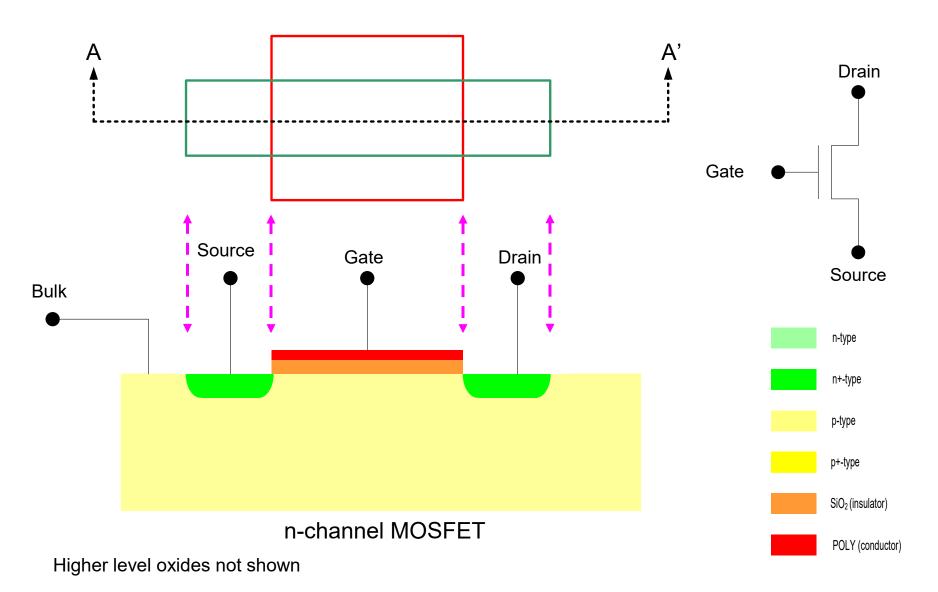

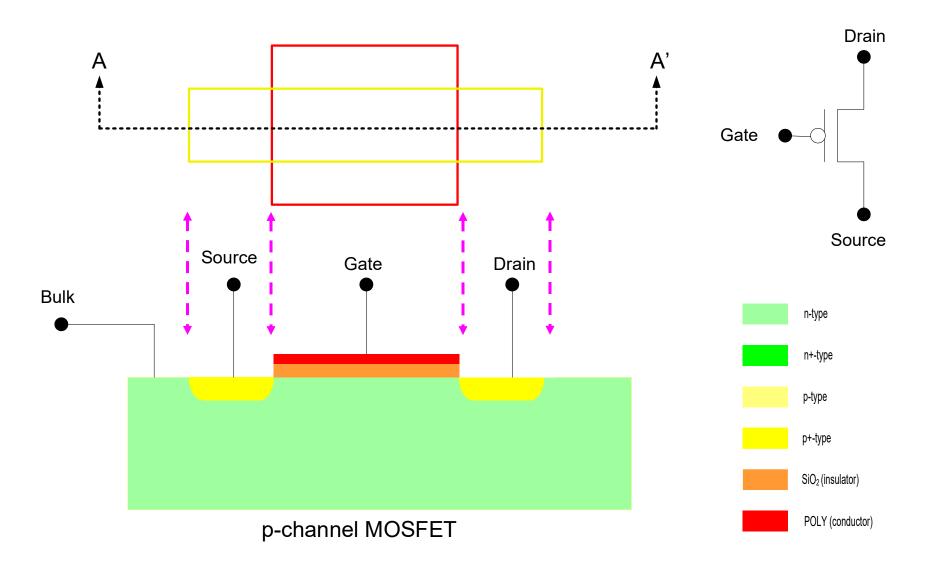

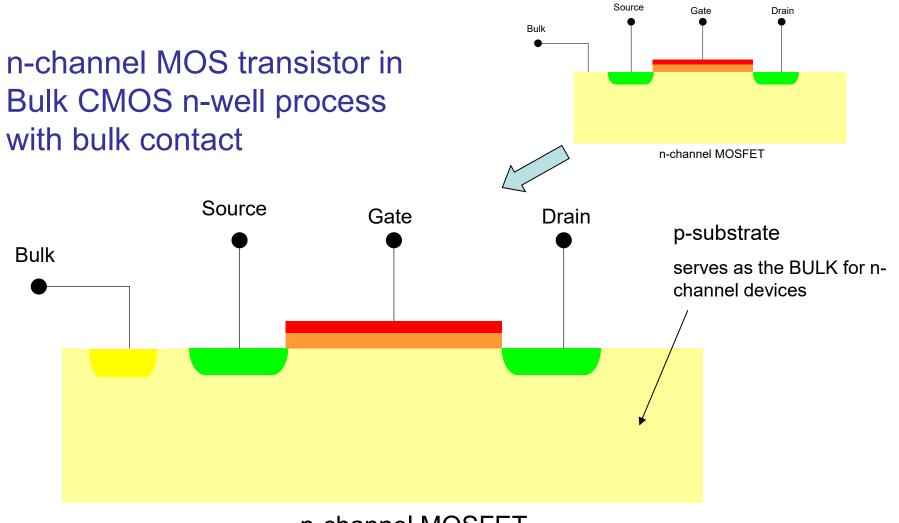

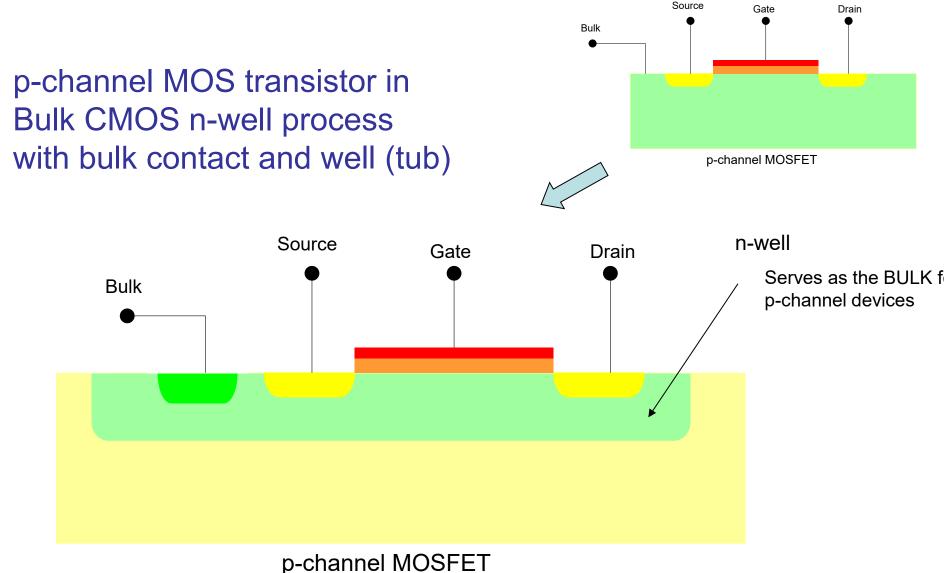

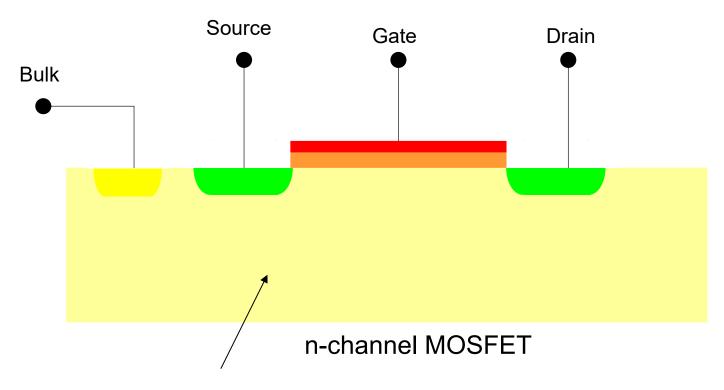

#### Review from Last Time MOS Transistor in Bulk CMOS Process

# Design Rules and Layout – consider transistors

- Bulk connection needed

- Single bulk connection can often be used for several (many) transistors

#### Table 5: Technology-code Map

|   | Technology<br>code<br>with link to<br>layer map | Layers                                                                                                                                                |

|---|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | <u>SCNE</u>                                     | <u>N_well, Active, N_select, P_select, Poly, Poly2, Contact, Metal1, Via, Metal2, Glass</u>                                                           |

|   | <u>SCNA</u>                                     | <u>N_well, Active, N_select, P_select, Poly, Poly2, Contact, Pbase, Metal1, Via, Metal2, Glass</u>                                                    |

|   | <u>SCNPC</u>                                    | <u>N_well, Active, N_select, P_select, Poly_cap, Poly,</u><br><u>Contact, Metal1, Via, Metal2, Glass</u>                                              |

|   | <u>SCN3M</u>                                    | N_well, Active, N_select, P_select, Poly, Silicide block<br>(Aqilent/HP only), Hi_Res_Implant, Contact, Metal1,<br>Via, Metal2, Via2, Metal3, Glass   |

| • | <u>SCN3ME</u>                                   | <u>N_well, Active, N_select, P_select, Poly</u> , <u>Poly2,</u><br><u>Hi_Res_Implant, Contact, Metal1, Via, Metal2, Via2,</u><br><u>Metal3, Glass</u> |

#### Select – Active(moat) Concepts

- Note that there is no n-active or p-active masks

- n-channel devices which need n-active are created by overlaying active with n-select

- p-channel devices which need p-active are created by overlaying active with p-select

- n-select and p-select masks are somewhat larger than the desired n-active and p-active regions

#### SCMOS Layout Rules - Select

| Rule | Description                                                                                                                           | Lambda |      |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|

| Kule | Description                                                                                                                           |        | SUBM | DEEP |

| 4.1  | Minimum select spacing to channel of transistor to ensure adequate source/drain width                                                 |        | 3    | 3    |

| 4.2  | Minimum select overlap of active                                                                                                      | 2      | 2    | 2    |

| 4.3  | Minimum select overlap of contact                                                                                                     | 1      | 1    | 1.5  |

| 4.4  | Minimum select width and spacing<br>(Note: P-select and N-select may be coincident, but must<br><i>not</i> overlap) (not illustrated) | 2      | 2    | 4    |

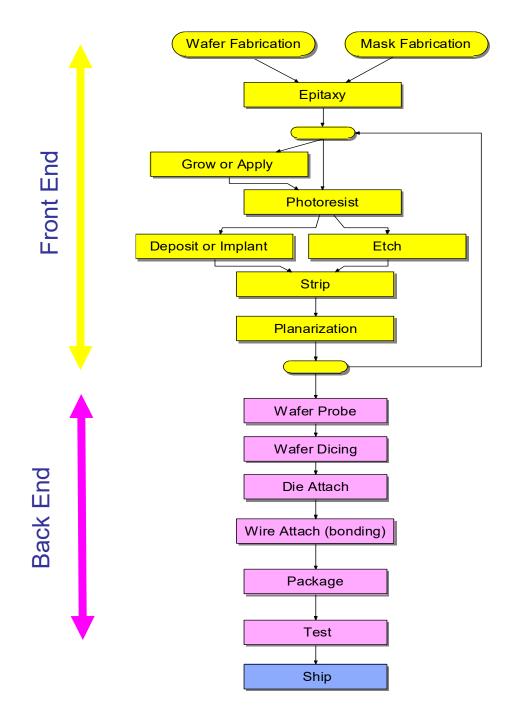

# **Technology Files**

Design Rules

Process Flow (Fabrication Technology)

• Model Parameters (will discuss in substantially more detail after device operation and more advanced models are introduced)

#### **IC Fabrication Technology**

#### See Chapter 3 and a little of Chapter 1 of WH

#### Generic Process Flow

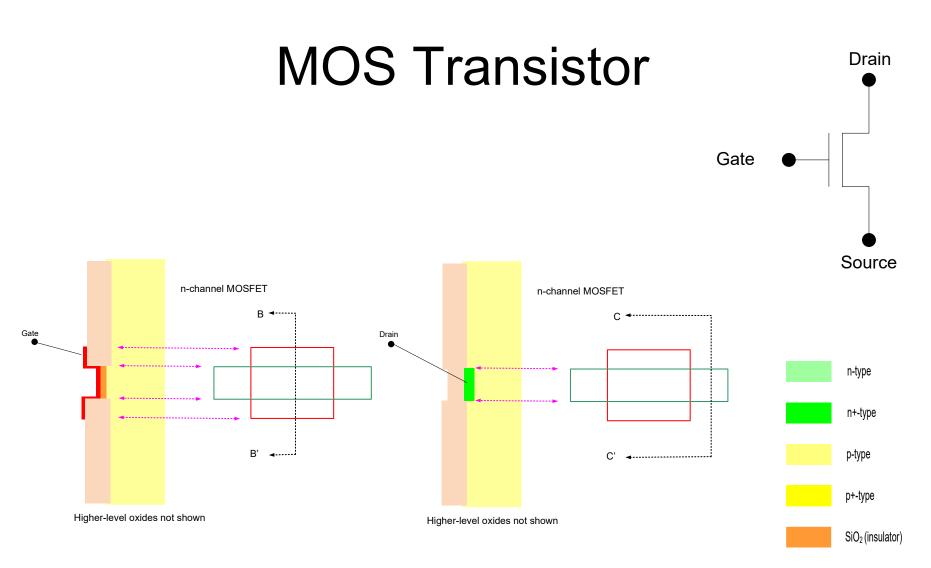

#### First a bit of background on transistor structure

#### First a bit of background on transistor structure

Looks Different on Other Cross-Sections !

Recall

POLY (conductor)

Review

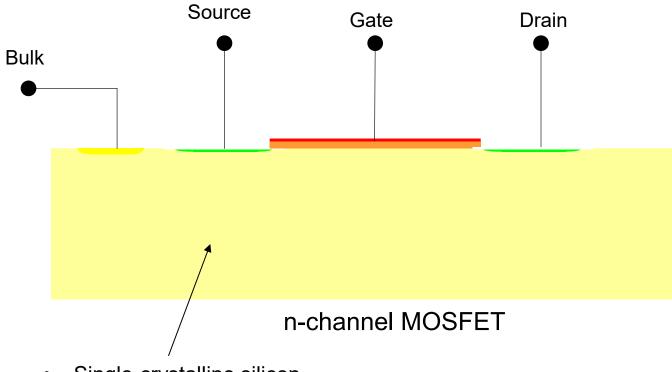

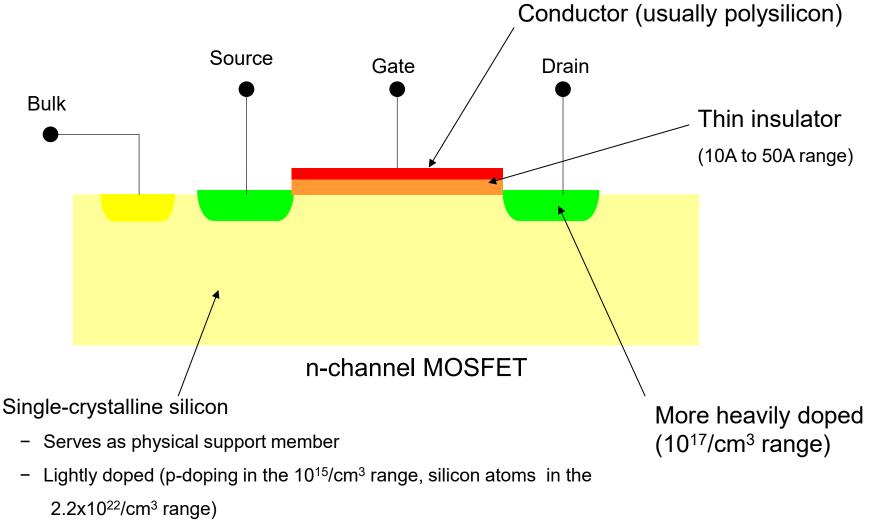

n-channel MOSFET

- Single-crystalline silicon

- Serves as physical support member

- Lightly doped

- Vertical dimensions are not linearly depicted

- Often termed the Bulk

- Single-crystalline silicon

- Serves as physical support member

- Lightly doped

- Vertical dimensions are not linearly depicted

- Often termed the BULK

- Vertical dimensions are not linearly depicted

- Often termed the BULK

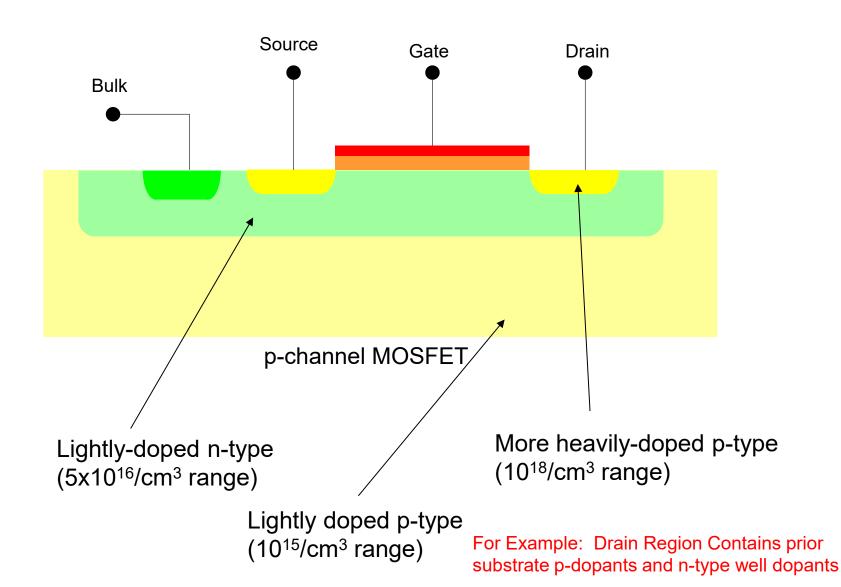

Dominant Doping Depicted – Generally Contain Prior Lower Density Dopants of Opposite Type

# IC Fabrication Technology

- Crystal Preparation

- Masking

- Photolithographic Process

- Deposition

- Ion Imlantation

- Etching

- Diffusion

- Oxidation

- Epitaxy

- Polysilicon

- Planarization

- Contacts, Interconnect and Metalization

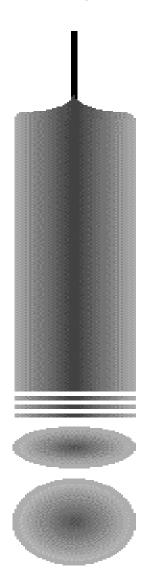

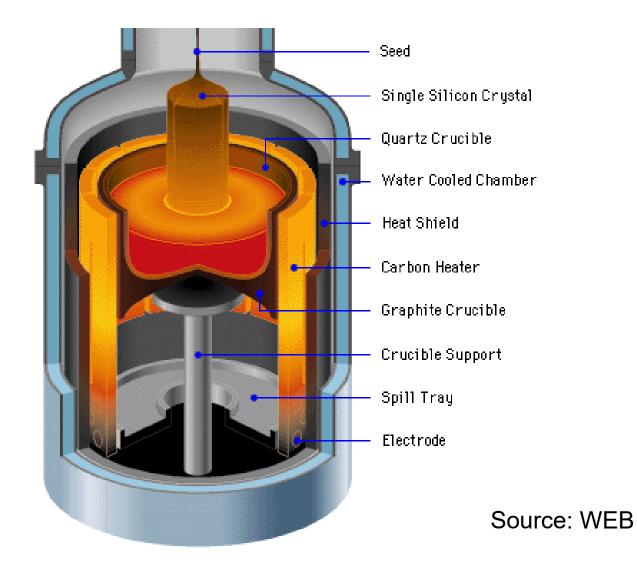

- Large crystal is grown (pulled)

- 12 inches (300mm) in diameter and 1 to 2 m long

- Sliced to 250 $\mu$ m to 500 $\mu$ m thick

- Prefer to be much thinner but thickness needed for mechanical integrity

- 4 to 8 cm/hr pull rate

- T=1430 °C

- Crystal is sliced to form wafers

- Cost for 12" wafer around \$200

- 5 companies provide 90% of worlds wafers

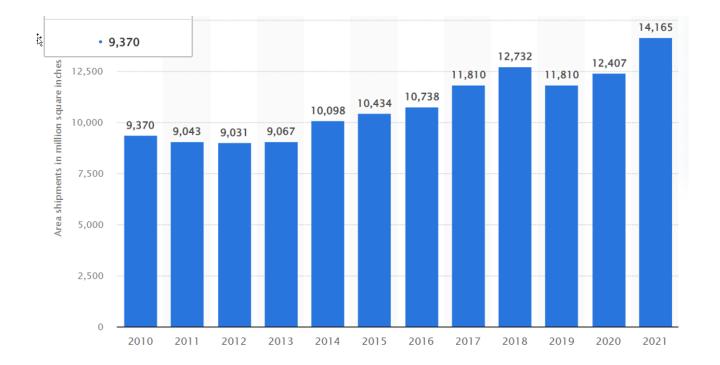

- Somewhere around 400,000 12in wafers/month

#### Silicon wafer area is a better metric

| Wafer size ◆                                               | Typical<br>Thickness <sup>♦</sup> | Year<br>Prodn ≑<br>[15] | Weight<br>per 🗢<br>wafer     | 100 mm2 [hide]<br>(10 mm) Die per  ✦<br>wafer |

|------------------------------------------------------------|-----------------------------------|-------------------------|------------------------------|-----------------------------------------------|

| 1-inch (25 mm)                                             |                                   | 1960                    |                              |                                               |

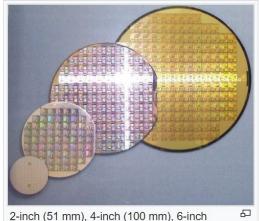

| 2-inch (51 mm)                                             | 275 µm                            | <mark>1969</mark>       |                              |                                               |

| 3-inch (76 mm)                                             | 375 µm                            | 1972                    |                              |                                               |

| 4-inch (100 mm)                                            | 525 µm                            | 1976                    | 10 grams<br>[19]             | 56                                            |

| 4.9 inch (125 mm)                                          | 625 µm                            | 1981                    |                              |                                               |

| 150 mm (5.9 inch, usually referred to as "6 inch")         | 675 µm                            | 1983                    |                              |                                               |

| 200 mm (7.9 inch, usually referred to as "8 inch")         | 725 µm.                           | 1992                    | 53 grams<br>[19]             | 269                                           |

| 300 mm (11.8 inch, usually referred to as "12 inch")       | 775 µm                            | 2002                    | 125<br>grams <sup>[19]</sup> | 640                                           |

| 450 mm (17.7 inch)<br>(proposed). <sup>[20]</sup>          | 925 µm                            | future                  | 342<br>grams <sup>[19]</sup> | 1490                                          |

| 675-millimetre (26.6 in)<br>(Theoretical). <sup>[21]</sup> | Unknown.                          | future                  |                              |                                               |

(150 mm), and 8-inch (200 mm) wafers

300mm wafer

450 mm wafer

# **Crystal Preparation** 1 to 2 m 12in 250u tp 500u Lightly-doped silicon Excellent crystalline structure

Some predicted newer FABs will be at 450mm (18in) by 2020 but appears to be uncertain whether it will ever happen

Return on Investment Essential to Make Transition

200mm (8") and 300mm (12") are dominant in production today

From www.infras.com

Source: WEB

A section of 300mm ingot is loaded into a wiresaw

Source: WEB

#### **Crystal Preparation**

Source: WEB

# IC Fabrication Technology

- Crystal Preparation

- Masking

- Photolithographic Process

- Deposition

- Ion Implantation

- Etching

- Diffusion

- Oxidation

- Epitaxy

- Polysilicon

- Planarization

- Contacts, Interconnect and Metalization

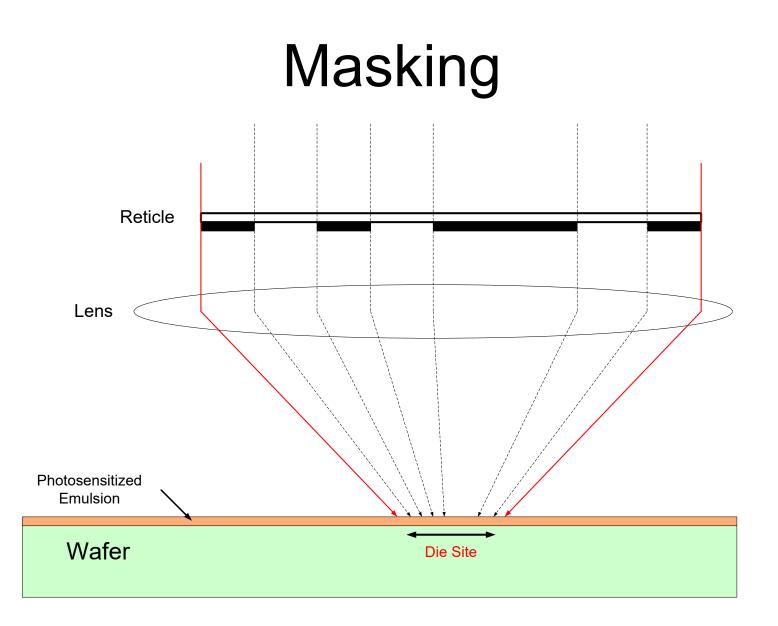

# Masking

- Use masks or reticles to define features on a wafer

- Masks same size as wafer

- Reticles used for projection

- Reticle much smaller (but often termed mask)

- Reticles often of quartz with chrome

- Quality of reticle throughout life of use is critical

- Single IC may require 20 or more reticles

- Cost of "mask set" now exceeds \$1million for state of the art processes

- Average usage 500 to 1500 times

- Mask costs exceeding 50% of total fabrication costs in sub 100nm processes

- Serve same purpose as a negative (or positive) in a photographic process

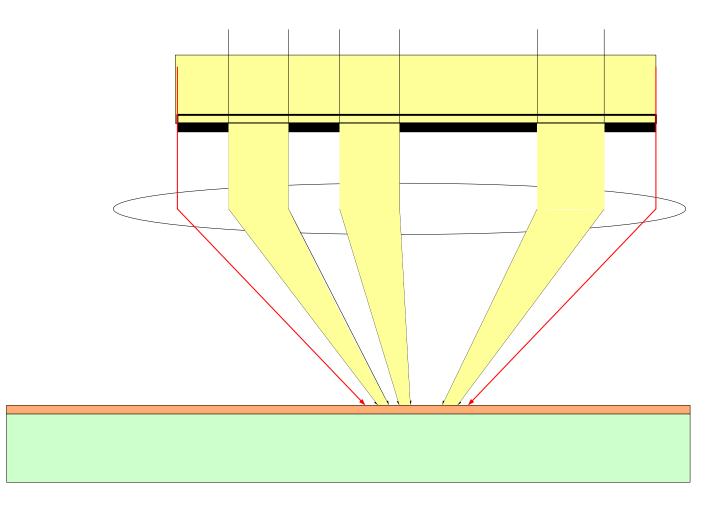

- Usually use 4X optical reduction exposure area approx. 860mm<sup>2</sup> (now through 2022 ITRS 2007 litho, Table LITH3a)

Step and Repeat (stepper) used to image across wafer

## Masking

#### Exposure through reticle

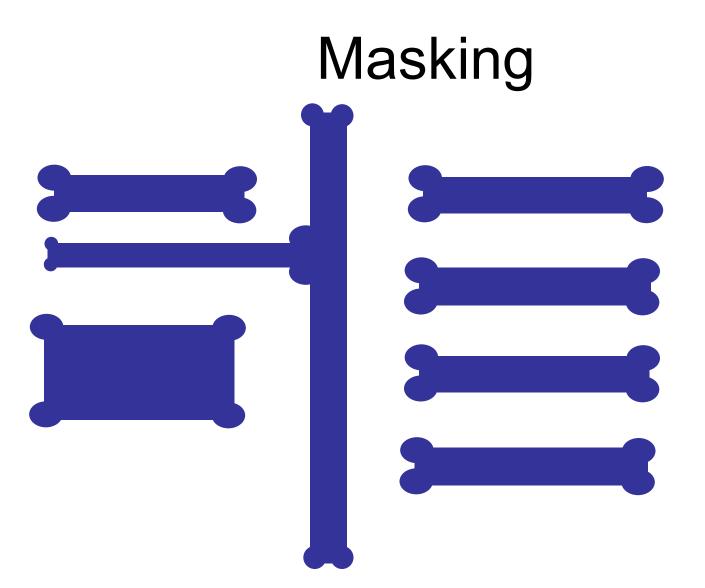

### Masking

#### **Mask Features**

Mask Features Intentionally Distorted to Compensated For Wavelength Limitations in Small Features

# IC Fabrication Technology

- Crystal Preparation

- Masking

- Photolithographic Process

- Deposition

- Ion Implantation

- Etching

- Diffusion

- Oxidation

- Epitaxy

- Polysilicon

- Planarization

- Contacts, Interconnect and Metalization

## Photolithographic Process

- Photoresist

- Viscous Liquid

- Uniform Application Critical (spinner)

- Baked to harden

- Approx 1u thick

- Non-Selective

- Types

- Negative unexposed material removed when developed

- Positive-exposed material removed when developed

- Thickness about 450nm in 90nm process (ITRS 2007 Litho)

- Exposure

- Projection through reticle with stepper (scanners becoming popular)

- Alignment is critical !!

- E-Bean Exposures

- Eliminate need fro reticle

- Capacity very small

Stepper: Optics fixed, wafer steps in fixed increments

Scanner: Wafer steps in fixed increments and during exposure both optics and wafer are moved to increase effective reticle size

#### Steppers

Stepper costs in the \$10M range with thru-put of around 100 wafers/hour

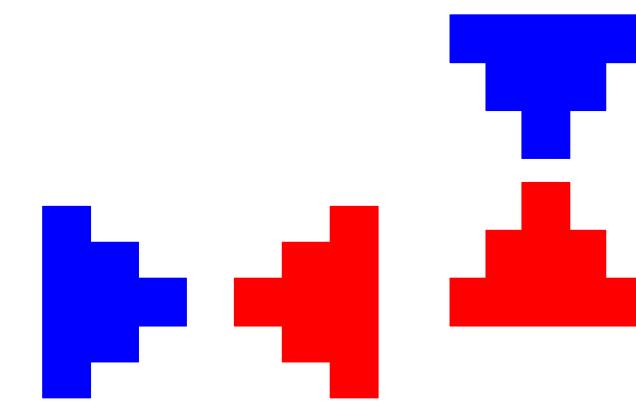

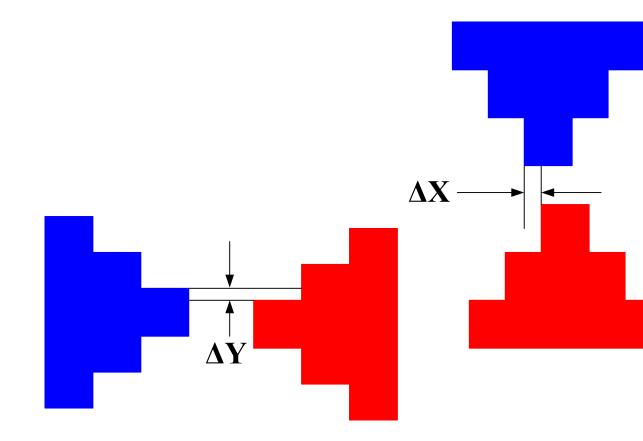

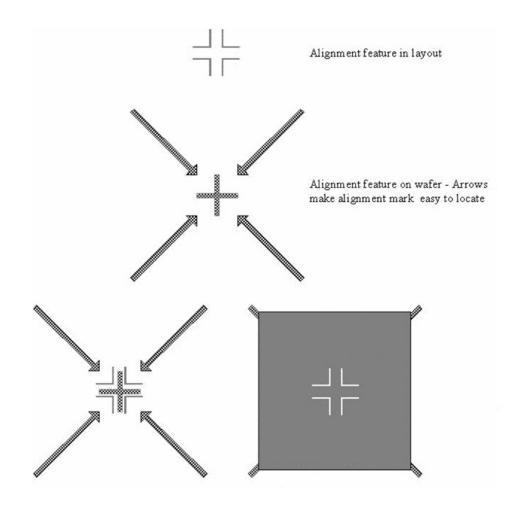

### Mask Alignment

#### **Correctly Aligned**

### Mask Alignment

#### **Alignment Errors**

### Mask Alignment

Other alignment marks (http://www.mems-exchange.org/users/masks/intro-equipment.html)

# IC Fabrication Technology

- Crystal Preparation

- Masking

- Photolithographic Process

- Deposition

- Ion Implantation

- Etching

- Diffusion

- Oxidation

- Epitaxy

- Polysilicon

- Planarization

- Contacts, Interconnect and Metalization

## Deposition

- Application of something to the surface of the silicon wafer or substrate

- Layers 15A to 20u thick

- Methods

- Physical Vapor Deposition (nonselective)

- Evaporation/Condensation

- Sputtering (better host integrity)

- Chemical Vapor Deposition (nonselective)

- Reaction of 2 or more gases with solid precipitate

- Reduction by heating creates solid precipitate (pyrolytic)

- Screening (selective)

- For thick films

- Low Tech, not widely used today

## Deposition

Example: Chemical Vapor Deposition

Silane (SiH<sub>4</sub>) is a gas (toxic and spontaneously combustible in air) at room temperature but breaks down into Si and H<sub>2</sub> above 400°C so can be used to deposit Si.

$S_iH_4 \rightarrow S_i + 2H_2$

# IC Fabrication Technology

- Crystal Preparation

- Masking

- Photolithographic Process

- Deposition

- Ion Implantation

- Etching

- Diffusion

- Oxidation

- Epitaxy

- Polysilicon

- Contacts, Interconnect and Metalization

- Planarization

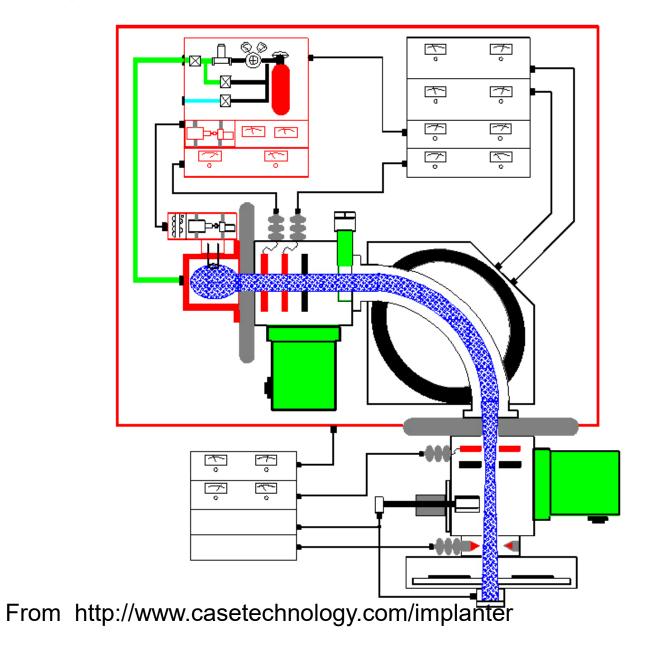

## Ion Implantation

Application of impurities into the surface of the silicon wafer or substrate

- Individual atoms are first ionized (so they can be accelerated)

- Impinge on the surface and burry themselves into the upper layers

- Often very shallow but with high enough energy can go modestly deep

- Causes damage to target on impact

- Annealing heals most of the damage

- Very precise control of impurity numbers is possible

- Very high energy required

- High-end implanters considered key technology for national security

#### **Ion Implantation Process**

#### Ion Implanter

From http://www.casetechnology.com/implanter

### Stay Safe and Stay Healthy !

# End of Lecture 9

# IC Fabrication Technology

- Crystal Preparation

- Masking

- Photolithographic Process

- Deposition

- Ion Implantation

- Etching

- Diffusion

- Oxidation

- Epitaxy

- Polysilicon

- Contacts, Interconnect and Metalization

- Planarization

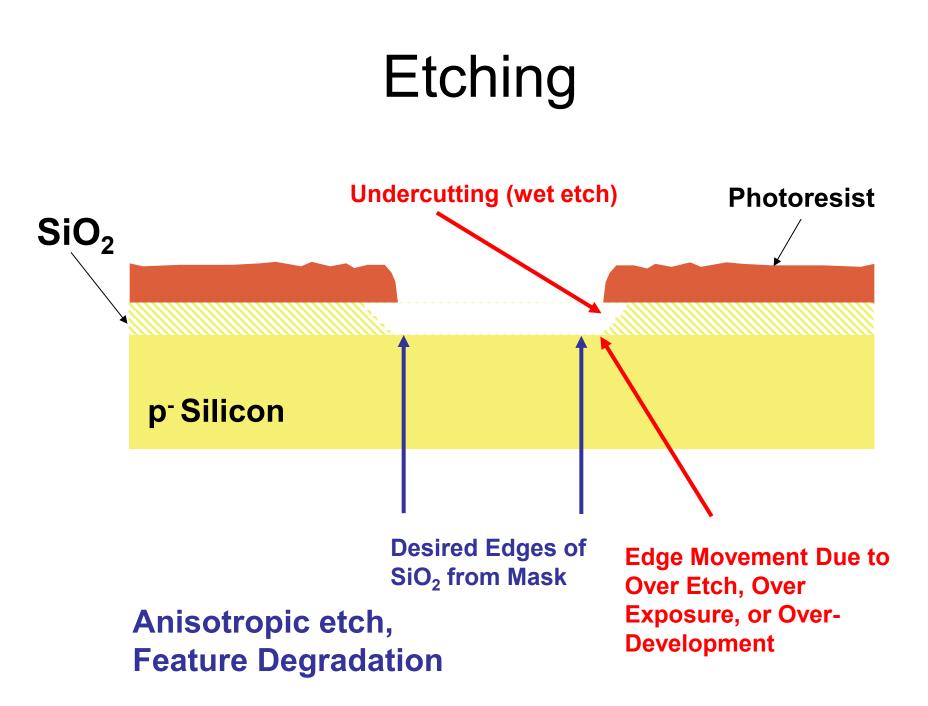

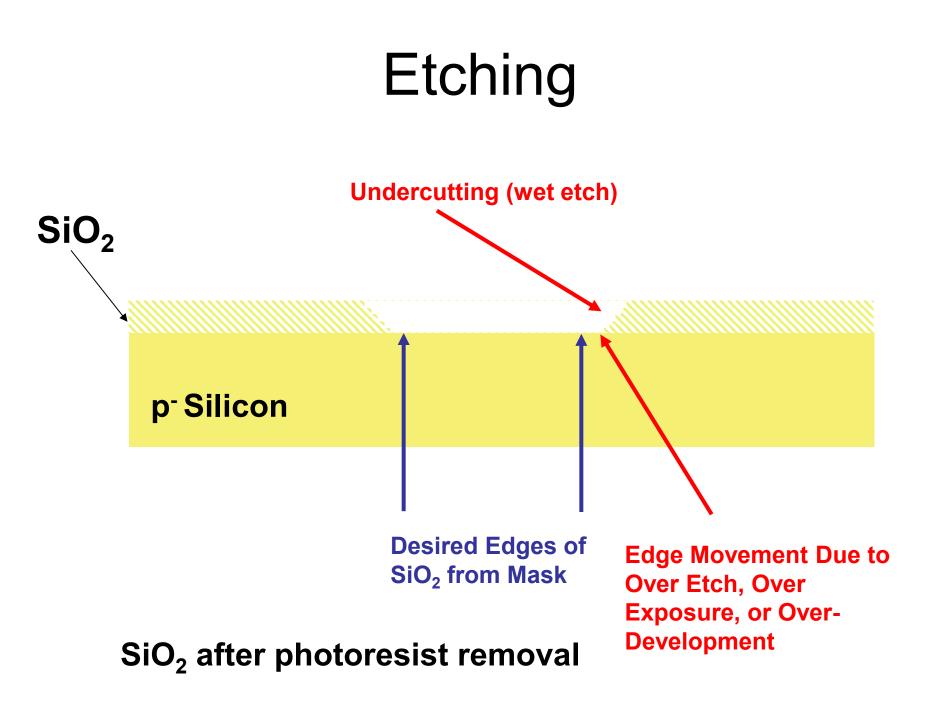

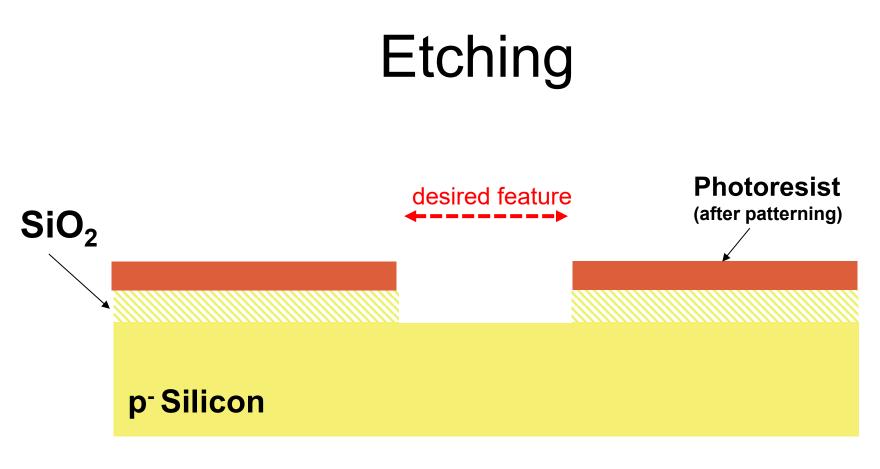

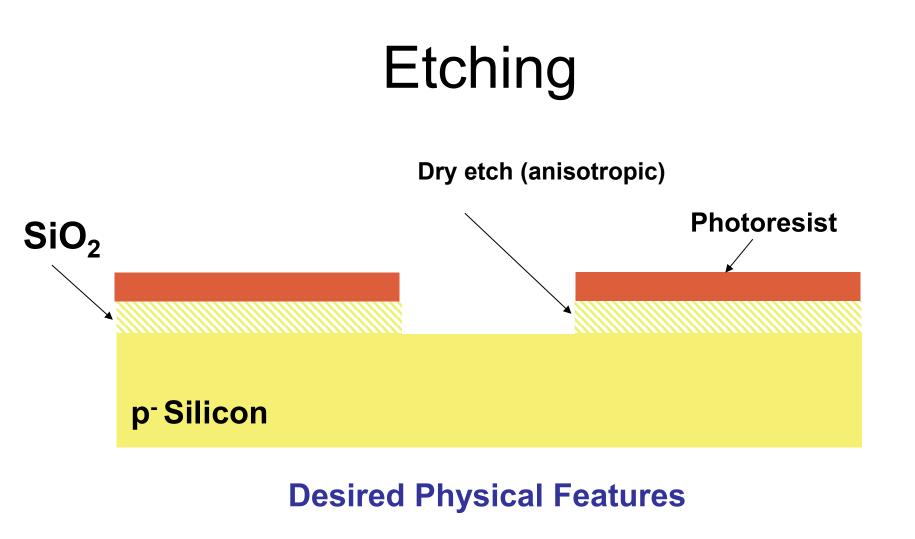

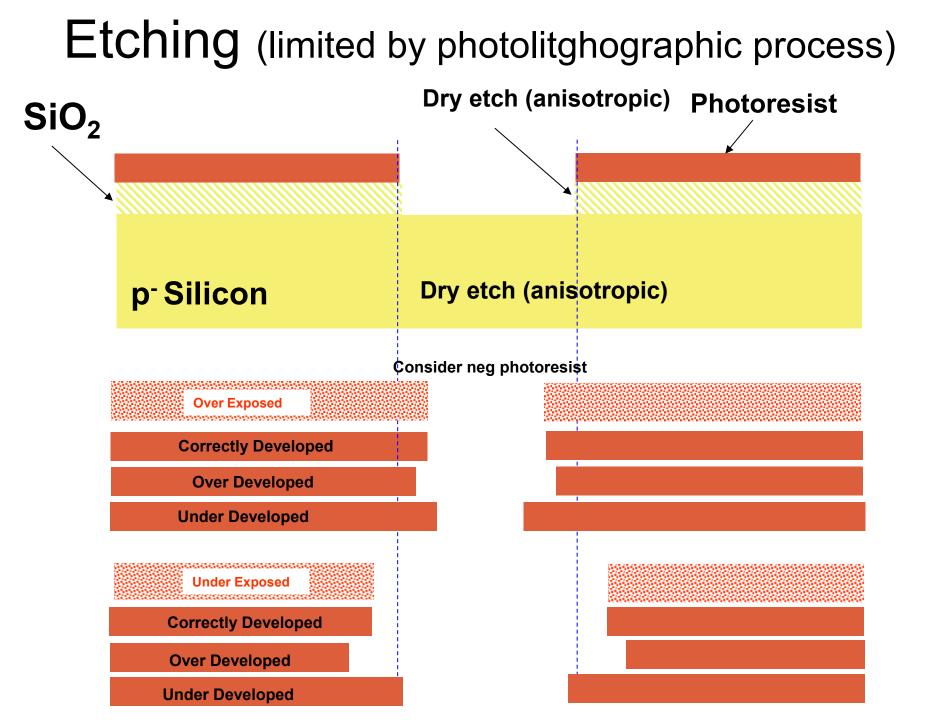

# Etching

Selective Removal of Unwanted Materials

• Wet Etch

– Inexpensive but under-cutting a problem

Dry Etch

– Often termed ion etch or plasma etch

#### **Desired Physical Features**

Note: Vertical Dimensions in silicon generally orders of magnitude smaller than lateral dimensions so different vertical and lateral scales will be used in this discussion. Vertical dimensions of photoresist which is applied on top of wafer is about  $\frac{1}{2}$  order of magnitude larger than lateral dimensions

Dry Etch can provide very well-defined and nearly vertical edges (relative to photoresist paterning)

For Example, the wafer thickness is around 250u and the gate oxide is around 50A (5E-3u) and diffusion depths are around  $\lambda/5$